LABORATORIO

|

|

E |

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

3 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

5 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

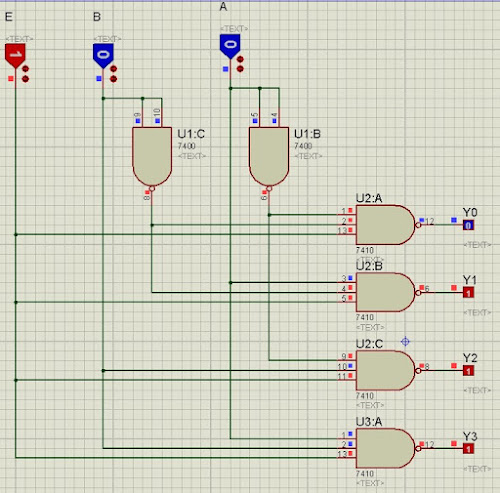

el decodificador

74hc154 tiene 4 entradas con una entrada de habilitación en nivel bajo, para

decodificar un numero de 5 bit utilizando el 74hc154, se puede utilizar la

entrada de habilitación como el quinto bit, en el primer codificador tendría

habilitación en nivel bajo y en el segundo una entrada de habilitación en nivel

alto.

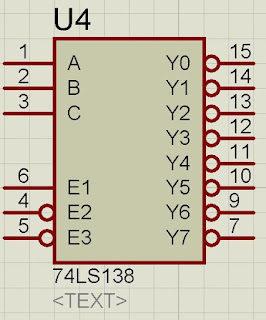

Una cierta aplicación requiere

decodificar un número de 4 bits. Utilizar decodificadores 74138 para

implementar el circuito lógico. El número binario se representa de la forma: A3A2A1A0 Realice y Simule su diseño y explique sus resultados.

La salida en nivel bajo se obtiene cuando las entradas de

habilitación E1, E2, E3 valen 1,0,0 respectivamente.

Para poder representar un numero de 4 bits se

tiene utilizar dos decodificadores 74138, conectar las entradas de habilitación E3, E2 a tierra

y E1 en nivel alto en primer de decodificador, este E1 también se tendrá que

conectar al segundo decodificador, pero con un inversor, de esta manera solo se

prendera uno de los dos. En el primer decodificador se mostrará los números

menores 8 y en el segundo se mostrarán del 8 al 15 en decimal.

Para

poder implementarlo se empleará un decodificador de 4x16, el decodificador 74hc154.

Ya

que el decodificador tiene salidas en nivel bajo lo que se hará es emplear

compuertas NAND, para que podamos obtener un 1 en la salida.

SIMULACION

0 Comentarios